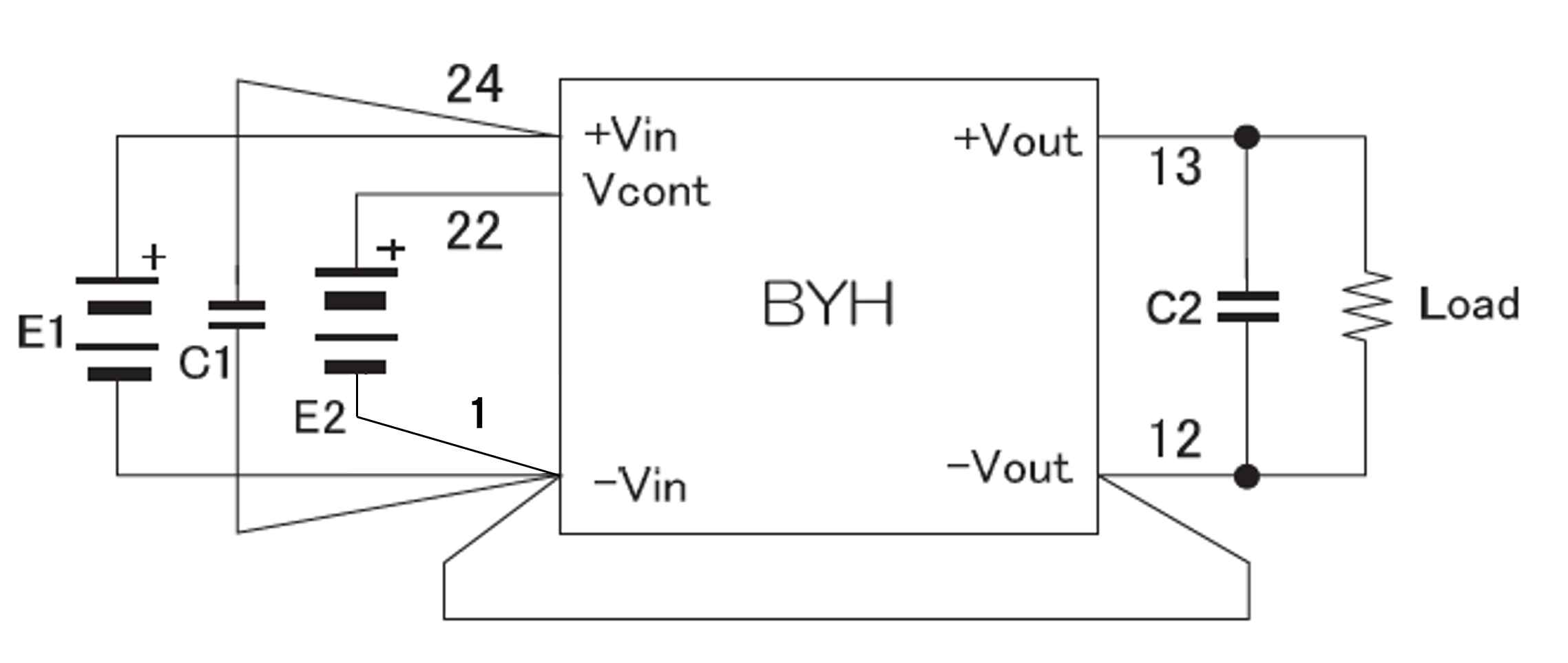

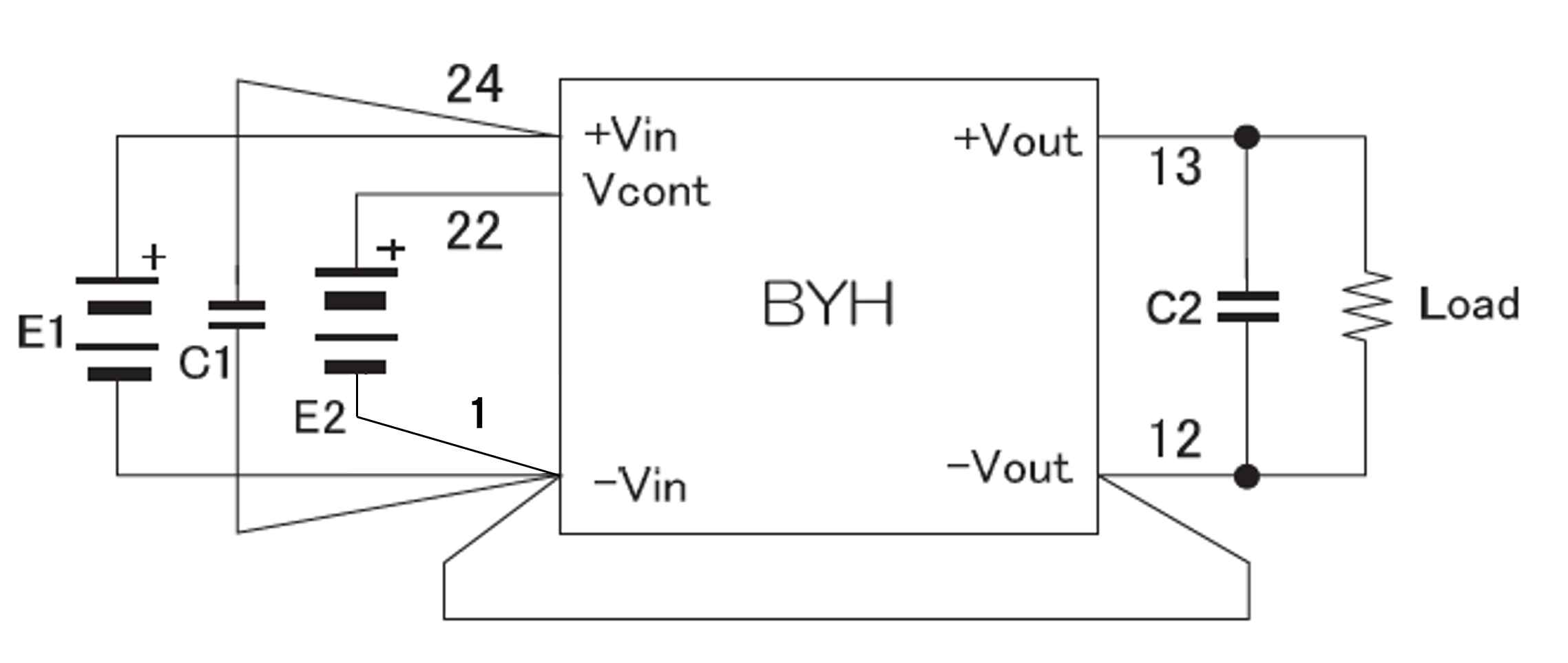

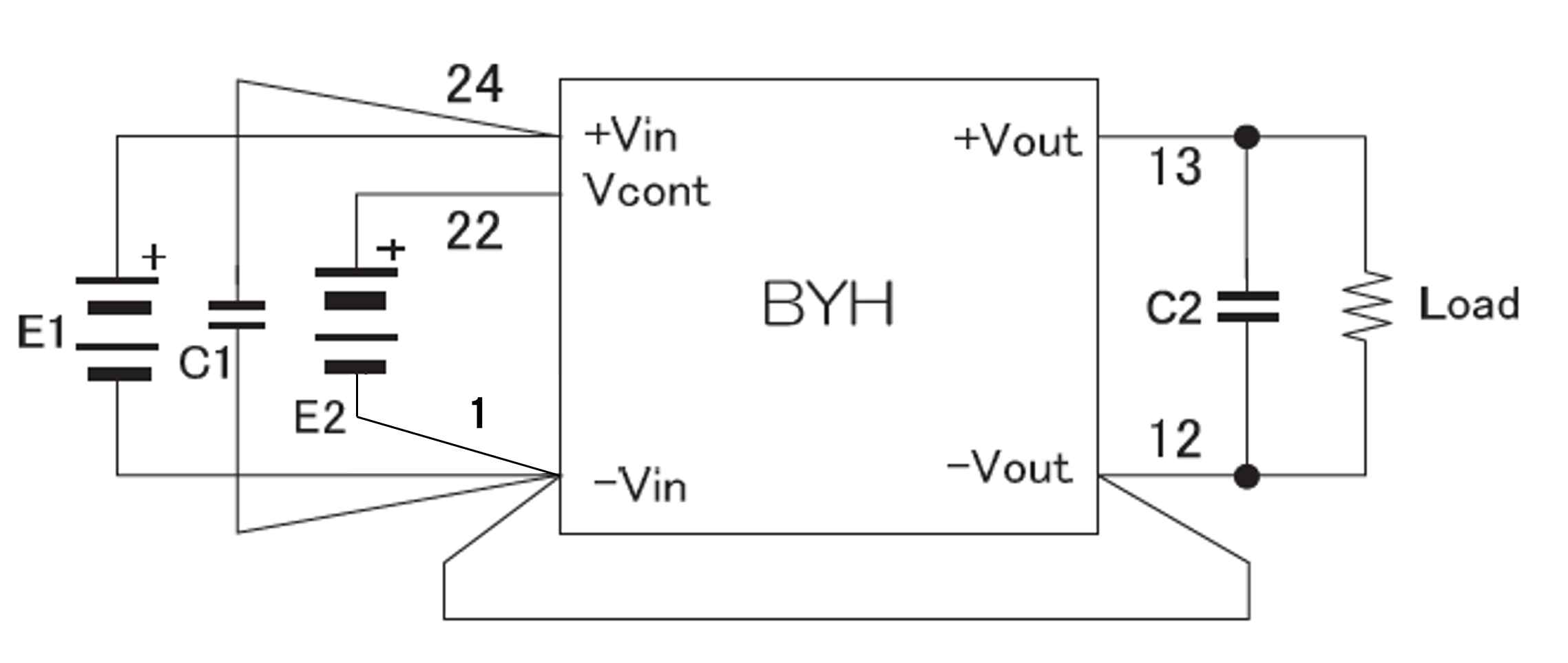

標準接続図

・推奨コンデンサ

C1=33μF~47μF(Electrolytic or Ceramic Capasitor)

C2=0.1μF(Ceramic Capasitor)

| Model | Input Voltage [VDC] | Input Current [mA](typ.) | Output Voltage Range [VDC] | Line Reg. [%](typ/) | Load Reg. [%](typ.) | Ripple Noise [mVpp](typ.) | Efficiency [%](typ.) | Size (WxDxH/mm) | Datasheet | Purchase |

|---|---|---|---|---|---|---|---|---|---|---|

| BYH05-100S02 | 4.75 to 5.25 | 90 | 0 to 100 | 0 to 2 | 0.3 | 10 | 0 to 3 | 32.6x20.42x10.3 | DigiKey chip1stop corestaff |

|

| BYH12-100S02 | 11.0 to 16.0 | 34 | 0 to 100 | 0 to 2 | 0 to 10 | DigiKey chip1stop corestaff |

||||

| BYH05-200S01 | 4.75 to 5.25 | 98 | 0 to 200 | 0 to 1 | 0 to 3 | DigiKey chip1stop corestaff |

||||

| BYH12-200S01 | 11.0 to 16.0 | 41 | 0 to 200 | 0 to 1 | 0 to 10 | DigiKey chip1stop corestaff |

注記:詳細につきましては、データーシートをご確認ください。

![]() 不使用証明書.pdf

不使用証明書.pdf

・推奨コンデンサ

C1=33μF~47μF(Electrolytic or Ceramic Capasitor)

C2=0.1μF(Ceramic Capasitor)