デカップリングコンデンサの量が少ない時は、その量を増やせば電源電圧の動的変動値を小さくすることができます。(出力インピーダンスを下げる)

電圧変動が発生する要因は下記が考えられます。

静的要因:基板上の配線抵抗による変動、電源の負荷変動

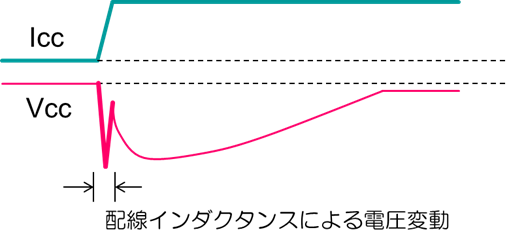

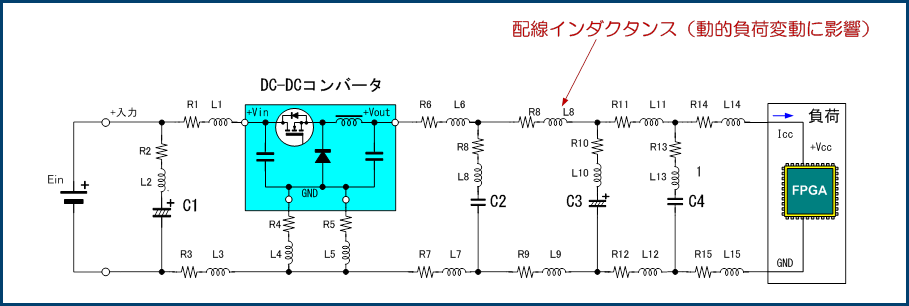

動的要因:基板上の配線インダクタンスによる影響、電源の動的負荷変動(応答速度)

静的な要因は、電流量で変化します。これは、基板の配線や選定した電源の特性なので基板設計時や部品選定時に要因を取り除く事ができます。電源の特性としては、“負荷変動” “Load reguration”といった形でデータシートに記されています。設計後でもパターンの上に銅バーをはんだ付けするなどの手段が考えられますが、製品化の面では現実的ではありません。

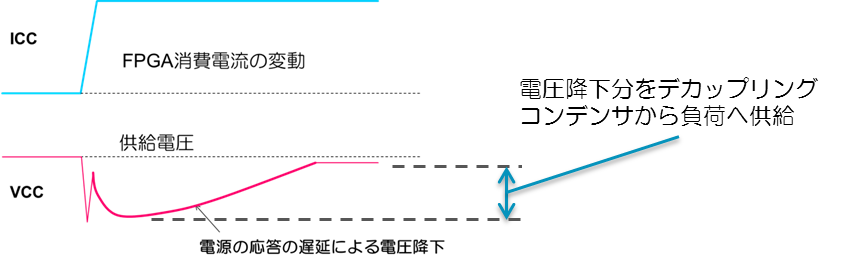

動的な要因は、急激な電流の変化で動的負荷変動として顕在化します。上図では、ICCが急激に変化した事でVCC供給電圧にディップが発生した様子を示しています。

デカップリングコンデンサ容量を増やす事で小さくできる可能性があるのは、動的要因による負荷変動(ディップ)になります。数百uF以上の容量の積層セラミックコンデンサや低ESRと言われるコンデンサをなるべくVCC端子に近い位置に配置する事で改善が望めます。

動的出力変動が発生した時のフィードバック制御において、パルス幅は基準電圧と出力電圧の差である誤差電圧で決まります。

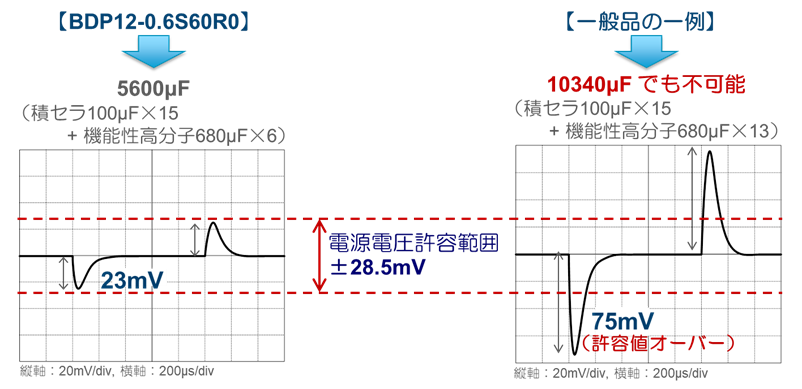

高速応答ではない一般的なPWM制御方式のPOLコンバータでは、出力電圧の変化に対して高速でパルス幅を開く事ができません。デカップリングコンデンサの量が大きいと出力電圧の変動が小さくなるためある程度追従できるようになります。しかしながら、電流の変化量と変化率が大きな場合は、デカップリングコンデンサがある容量以上になるとコンデンサを付け加えても動的変動が変わらなくなります。

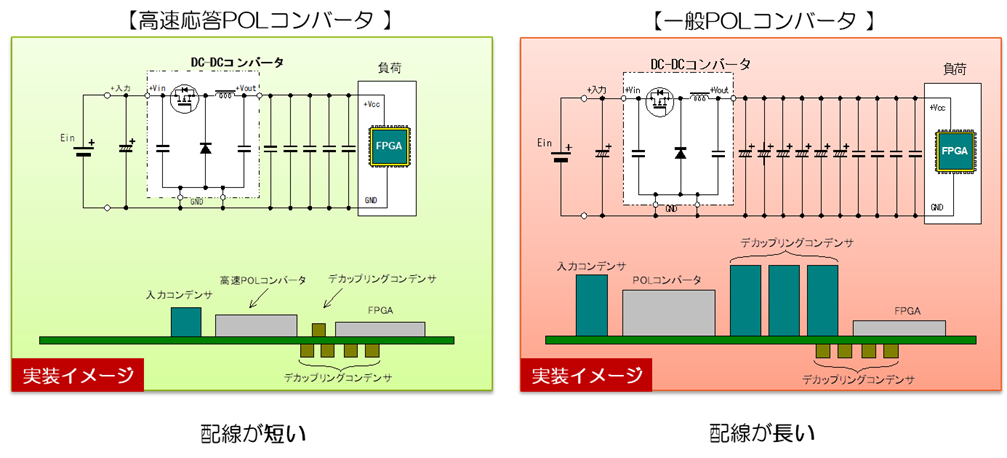

① 実装面積が大きくなる。

② POLコンバータ – FPGA間の配線が長くなる。

配線インダクタンスによる電圧変動は、非常に高い周波数成分のためセンシングしてもPOL コンバータで減衰させることができません。高周波特性の優れた積層セラミックコンデンサ をFPGA近傍に付加することでこの変動を抑えることができますが、配線が長すぎる場合は 抑えきれずFPGAの許容値を超えてしまいます。

安心の為にも、FPGA向けとしてリリースされているPOLコンバータを選定される事をお勧めします。 高速負荷応答をうたった物が望ましいと考えております。これらのコンバータであれば、ICメーカーの推奨値の容量を付加する事で大抵の場合、問題無く動作するようです。逆に言えば、極力応答速度の速いコンバータを選定する事で付加するコンデンサ容量を減らす事ができるようになります。基板の小型化、コンデンサ使用数の削減が望めます。

やはり、高速POLコンバータが必要です。