基板設計時に電源周りで気を付けたいこととしては以下が挙げられます。

- POLコンバータはFPGAの直近に配置したい。

- 電源ラインの配線は、流す電流量と電圧を考慮してなるべく太く短くしたい。

- 大電流が流れるラインは放熱の為にも配線インダクタンス低減の為にも表面層がベター。

- POLコンバータの要求する入出力コンデンサは、POLの直近に、同じ面で配置したい。

- FPGA要求のコンデンサは、FPGA直近に配置したい

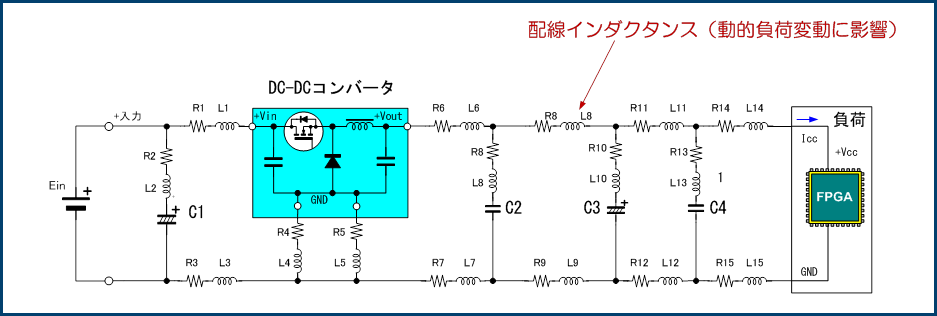

配線が細い:配線の抵抗値UP ⇒ 電圧ドロップ増加

配線が長い:配線の抵抗値UP ⇒ 電圧ドロップ増加

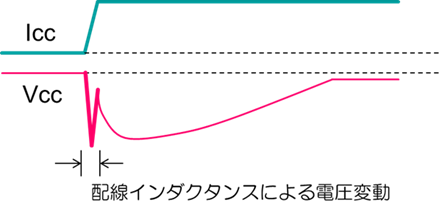

配線のインダクタンス増加 ⇒ 動的負荷変動悪化

スルーホールの使用:配線インダクタンスの増加

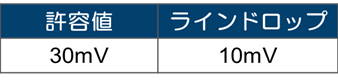

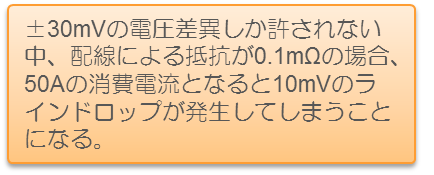

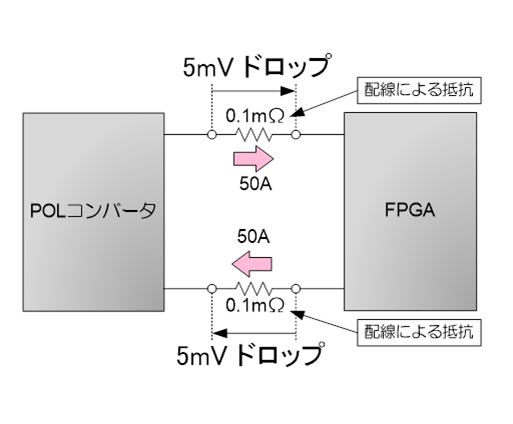

プリント基板上の銅箔パターンによる配線が長いとラインドロップ ( 電圧降下 ) により、FPGA の電源端子電圧は低下します。FPGA のコア電圧 ( VCCINT ) が低電圧の場合、電源電圧の許容範囲が小さく、配線パターンによる電圧降下を無視できません。

【例】 Virtex UltraScale FPGAのコア電圧( VCCINT)の許容電圧範囲は1.0Vデバイスで1.0V±3%(±30mV)です。

配線インダクタンスにより、負荷急変時電圧変動が発生します。FPGAの近傍に周波数特性の良い積層セラミックコンデンサを付加することである程度この変動を抑えることができますが、配線が長すぎる場合はFPGAの許容値を超えてしまいます。

POLコンバータには多かれ少なかれ入出力につける推奨コンデンサがあります。これらは、直近に配置する事により、POLの特性を発揮できます。

一つのバス電圧に複数のPOLがつながる場合は、入力側コンデンサをそれぞれのPOL直近に配置するよう特に配慮が必要です。これはPOLが入力コンデンサを要求していない場合でも搭載できるようにする方が無難です。

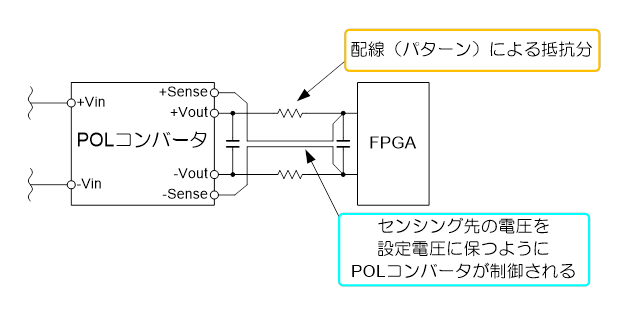

POLコンバータにはリモートセンシング端子を備えているものがあります。リモートセンシング機能を用いるとセンシング先の電圧が設定値となるよう制御されますので、配線パターンのドロップによる電圧降下が出力電圧に現れなくする事ができます。

・±それぞれのセンシングラインは寄り添うようにセンシングポイントまで配線して下さい。

・センシング先は、大容量のコンデンサの両端として下さい。

但し配線パターンの抵抗により消費する電力損失はそのままです。負荷急変時における配線インダクタンスによる電圧変動は、高周波のためコンバータで圧縮することができず、センシングの効果がありません。

また、センシングポイントとPOL出力端子間の電位差が大きすぎると、POLがOV保護で停止する恐れがあります。

従って、配線パターンは極力太く短くする事が最善の対策になります。

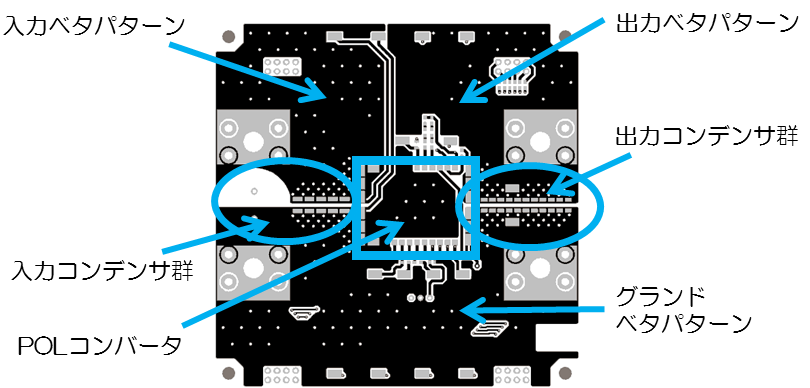

FPGA-POLコンバータ間の出力パターン、及びグランドパターンは可能な限り太く短いベタパターンとし、電流の流れを考慮してスルーホールを設ける必要があります。

下は、弊社製 BDP12-0.6S60R0評価ボードの配線パターン(表層のみ)です。使用する電源の推奨パターン図を参考に配線してください。