FPGAはプロセスルールの進化に伴って、高密度化が可能となり、高速、高機能化が進んでいます。プロセス技術の進歩により高密度化を実現する為に、FPGAに供給する電源の低電圧大電流化が進んでいます。 コア電圧の低電圧化はFPGAの高速化と低消費電流(低損失)化の為には有効ですが、電圧が高く電流量が少なかった昔では考えられなかった事が問題としてとらえられるようになってきました。

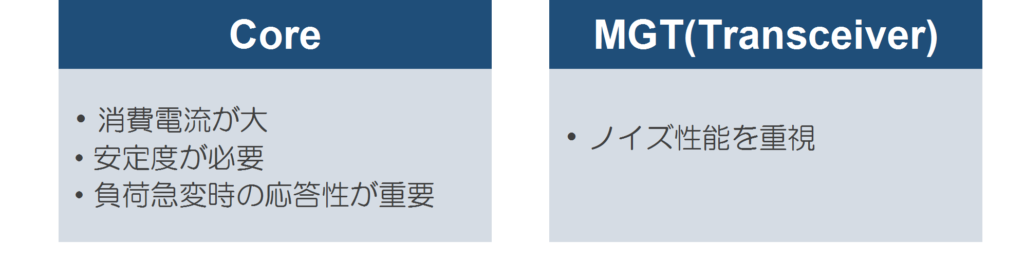

- 各電源ラインの電流値の予測

- 低電圧大電流が必要な電源ライン

- 高速応答が必要な電源ライン

- 低ノイズが要求される電源ライン

このことが、FPGA周りの電源設計を難しくしており、トラブルの原因となっています。

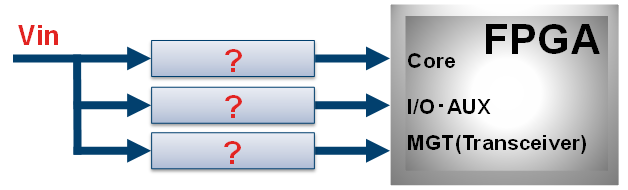

FPGAは一般的に複数の電源電圧が必要です。電源設計によるトラブルを減らし、FPGAの高いパフォーマンスを 最大限に引き出すためには、どのような電源選択、電源設計が必要となるでしょうか?

FPGAボードでの電源トラブルを無くすために電源も進化しています。 電源電圧が5Vや3.3Vで消費電流がそれほど多くない時代では、FPGAが要求する電源電圧の許容範囲も十分に広く、電源電圧はデジタルマルチメーターなどで測った値でほぼ一定と考えてもあまり支障がありませんでした。

また、FPGAに各電圧を供給するDC-DCコンバータは発熱部品ですので、FPGAの温度を煽らないようボードの入力端子付近にまとめて配置する集中給電が主流でした。

その後、電源電圧が下がってきて、電流量が多くなると、パターンでの電圧降下が無視できなくなりはじめ、DC-DCコンバータを負荷(FPGA)の近くに配置する分散給電方式に変わってきました。 負荷(FPGA)の近くは信号ラインがかなりのスペースを占める事と、FPGA自体が発熱するので、DC-DCコンバータを実装するには、小型であること、高効率で発熱が少ないことが重要な要素となります。 そこで、負荷の近くに実装することを目的とした非絶縁型のコンバータが開発され、小型、高効率で理想的な分散給電が可能となりました。 POLコンバータが生まれた後も、様々な問題解決の為に特徴を持ったPOLコンバータが生まれてきました。

このように負荷(FPGA)のすぐ近くに実装することをPOL(point of Load)といい、その為のDC-DCコンバータをPOLコンバータと呼んでいます。 本資料ではFPGAへの供給電源を“電源”または“POLコンバータ”と呼びます。

FPGAコア電圧の低下により、許容電圧範囲が狭くなったこと、消費電流の増加、及び高速動作による急激な電流変化などがトラブル要因となっています。 例えば5Vで±3%で良かったころは、電源ラインの電圧はFPGAの端子にて±150mV許容されていました。 単純に電源ライン電圧が1Vになると、許容電圧範囲は±30mVと桁違いに小さくなります。 電圧が下がると電流量が増えるので、配線の抵抗値の影響が無視できなくなってきます。 配線抵抗が1mΩで10A流れたとするとそれだけで10mV変動してしまうので、1Vラインの場合は30%近く変動してしまう事になります。この電圧の変動分を負荷変動、もしくは“静的負荷変動”と呼びます。

“静的負荷変動”は、この配線に起因する負荷変動と、電源のデータシートにある負荷変動の合算になります。 また、FPGAのCore端子に流れ込む電流は、急激に変化する為、電源の負荷応答特性も無視できなくなってきました。 電源電圧が高かった頃はコンデンサをFPGAそばに配置する事で改善できた電圧ディップも、電圧が下がってきたことでそれだけでは対応できなくなるケースも出てきました。 このような急激な電流値の変化により発生する負荷変動を“動的負荷変動”とよびます。

“静的負荷変動”と“動的負荷変動”を合わせて、許容電圧範囲内に電源ラインの電圧を抑える必要があります。