FPGAに供給する電源ラインの電圧は、様々な条件によって所望の設定値から変動します。

◆配線要因

- 電源ラインにぶら下がっている負荷の数

- 負荷の電流量(配線の抵抗値)による、配線での電圧ドロップ

- 負荷急変による配線の動的負荷変動分(配線のインダクタンス成分によるもの)

◆電源要因

- POLコンバータの設定精度と変動分

- 負荷急変によるPOLの動的負荷変動分(電源の応答速度によるもの)

◆ 電源電圧の設定精度(偏差)

POLコンバータの出力電圧は、製造時の部品バラつき等により、設定値から 多少のズレが生じます。

これがPOLコンバータの出力電圧設定偏差です。

◆ 電源電圧の総合変動

POLコンバータの出力電圧の総合変動は、一般的に次の3つから成ります。

- 入力電圧の変化に対する出力電圧変動 : 入力変動(Line Regulation)

- 出力電流の変化に対する出力電圧変動 : 負荷変動(Load Regulation)

- 周囲温度の変化に対する出力電圧変動 : 温度変動(Tempareture Regulation)

これらの電圧変動は、FPGAコア電圧の許容範囲を超える要因になります。

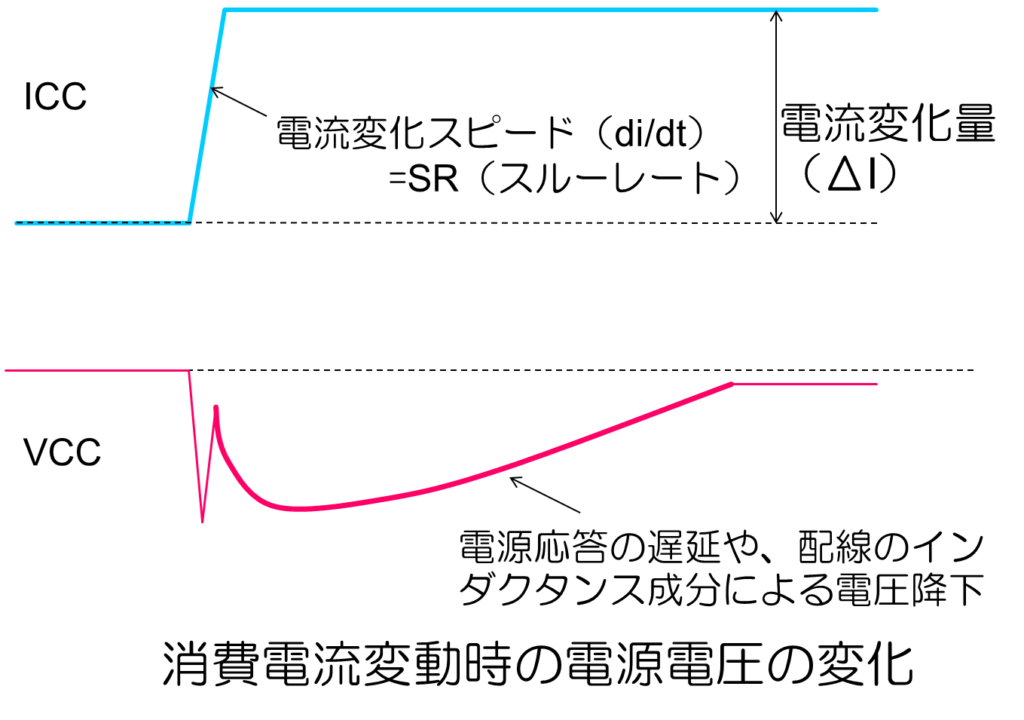

◆ 電源圧の動的変動

※ 消費電流急変時の電源応答特性は、使用するPOLコンバータやデカップリングコンデンサ、配線長等に左右されます。

◆配線要因

- 電源ラインの配線を太くする(抵抗値を可能な限り下げる)

- POLコンバータと負荷(FPGA)の間のハイセを極力短くする(抵抗値、インダクタンス値を極力小さくする)

- 効果的にパスコンを配置する

◆電源要因

- 出力電圧設定精度、及び総合変動の小さいPOLコンバータを選択する

- 負荷過渡応答速度の速いPOLコンバータを選択する

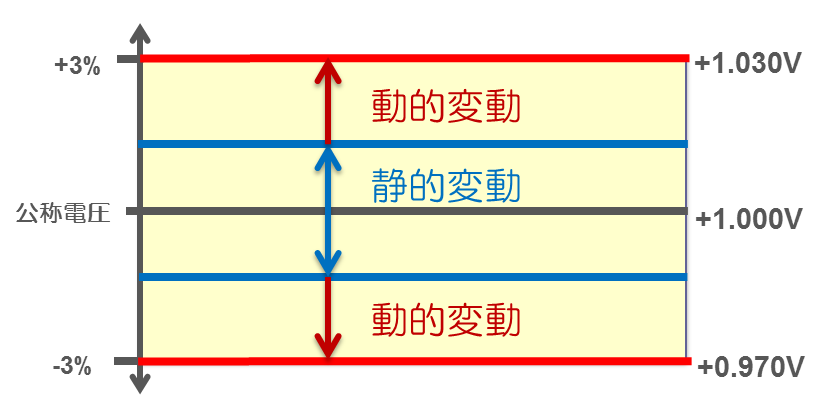

電源の出力電圧は、静的変動 と 動的変動の両方を含めてFPGAコア電圧の推奨動作電圧範囲内である必要があります。 Virtex Ultra Scale の場合、変動分が想定しにくい動的負荷変動等を考慮すると、事前に変動分が想定できるPOL コンバータの出力電圧設定精度は、少なくとも±1%以内に収めておきたいところです。その上で静的な変動分の小さい、 応答速度の速いコンバータを選択し、基板上の配線を太く短くする必要があります。 そうしないと、FPGAが電源に要求する許容電圧範囲±3%以内の実現は難しいと考えられます。

FPGAの供給電源電圧に求められる推奨動作範囲

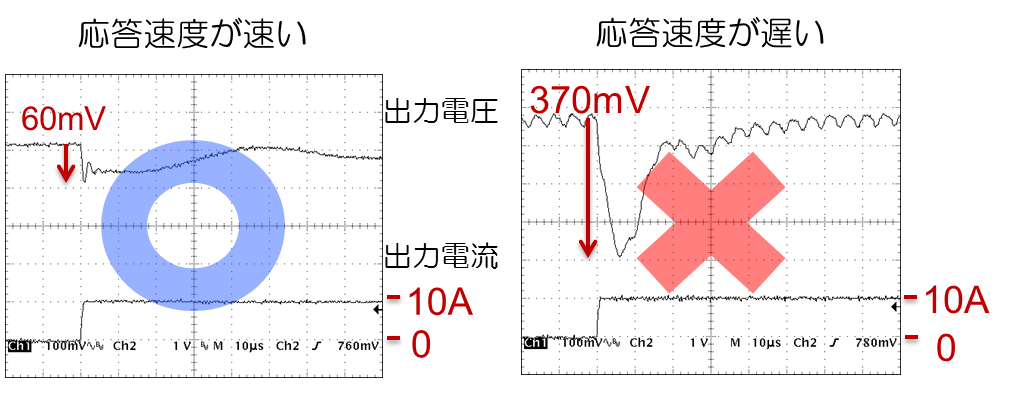

負荷過渡応答特性は、動的負荷変動、またはトランジェントと呼ばれることもあります。負荷過渡応答速度は、POLコンバータによって異なります。応答速度の遅いPOLコンバータを使用すると、動的負荷変動が大きくなります。

POLコンバータの出力電圧波形

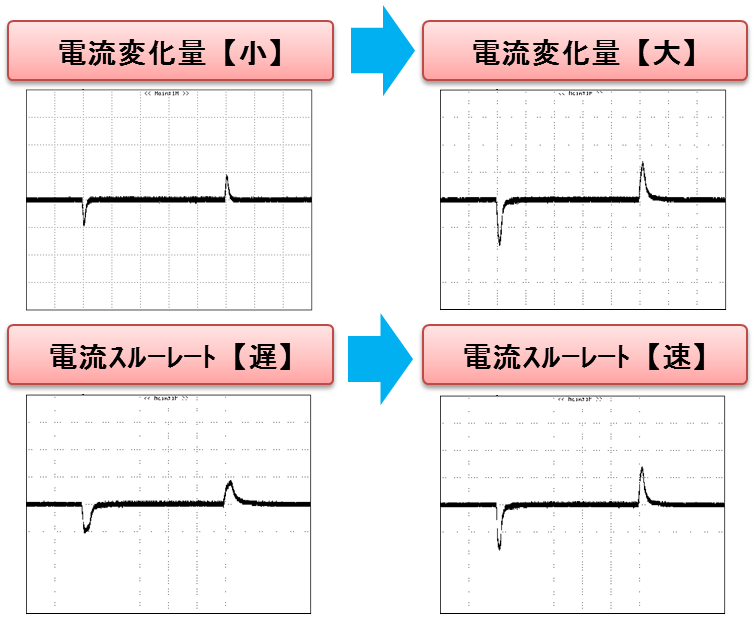

次の2項目で負荷過渡応答時の変動幅が変わります。

① 消費電流の電流変化量(ΔI)

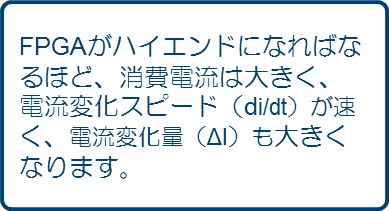

② 電流変化スピード(di/dt)= 電流スルーレート(SR)