FPGA を正常に立ち上げるためには、電源電圧の立ち上がり順序 ( シーケンス ) の要求があり、FPGAの指定した順序で電源電圧を立ち上げる必要があります。

このシーケンスを守らないとFPGA立ち上げ時に必要以上の突入電流(ラッシュ電流)が流れることがあります。

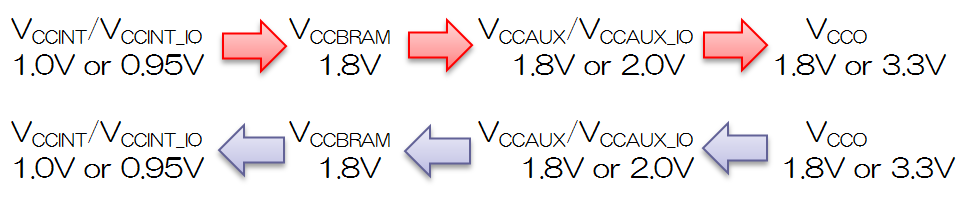

≪ 要求シーケンス例 : Virtex Ultra Scale ≫

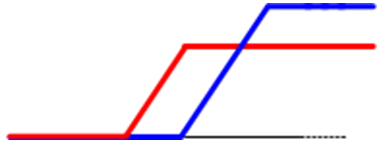

この例では、電源電圧の低い方から立ち上げ、電源電圧の高い方から立ち下げます。

※ 消費電流急変時の電源応答特性は、使用するPOLコンバータやデカップリングコンデンサ、配線長等に左右されます。

POLコンバータは大抵、出力電圧が正常に立ち上がった事を知らせるP-Good端子、出力のon/offをコントロールする為のon/off端子を機能として持っています。これらを使う事でシーケンスを組む事ができます。先に起動するコンバータのP-Good端子と後から起動するコンバータのon/off端子を適当な回路で接続する事でシーケンスを実現可能です。on/off端子-GND間にコンデンサを入れる事でタイミングをずらす事もできます。

シーケンスがあまりにも複雑な場合は、シーケンス・コントローラーを使用する事も考えられます。

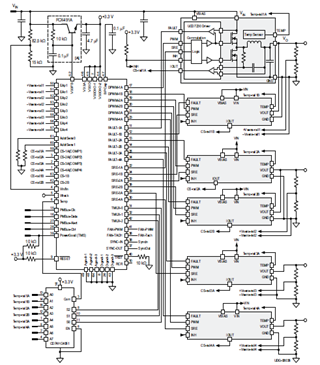

◆アナログPOLコンバータ + シーケンス・コントローラで構成した場合の回路例

シーケンス回路を組むにあたり、下記注意が必要です。

- 信号線にノイズが乗らないように引き回しを工夫する。

- on/off端子のインピーダンスが高い時は、CRのフィルタをコンバータ直近で組むようにする。

- シーケンスを組むコンバータ同士で動作時にGNDレベルがずれないようにする。(配線のインピーダンスが小さくなるように配慮した設計をする)

on/off端子は閾値が高いのでめったにノイズで誤動作する事は無いと思いますが、安心の為に配慮は必要になります。また、ボード上 に多数のPOLが存在し、それらが複雑に絡み合う場合は、配線が複雑になるので、引き回しに注意が必要です。

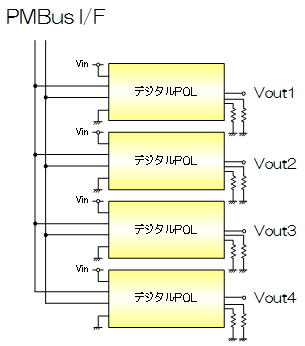

◆シンプルな回路構成

弊社デジタルコンバータであれば、外付け部品を一切接続する事なく電圧の傾斜も含めた複雑なシーケンスの作成が可能です。または、全てのコンバータを同一のPMBusラインにぶら下げて頂く事で、それぞれのコンバータの設定を外付け部品を変更する事なく修正する事ができるようになります。毎回PMBusにてon/offをコントロールする事も可能ですが、修正頂いた設定は保存できますので条件が毎回変わらないようであればこちらの機能も合わせてご利用下さい。また、量産時にご要求の設定を書き込んだ状態で出荷するサービスも行っております。合わせてご利用ください。

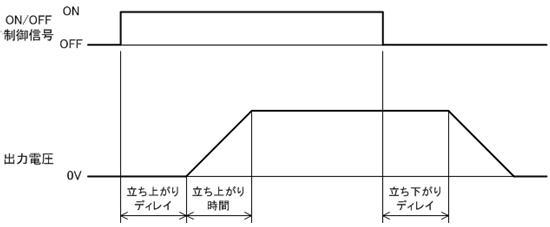

PMBus通信により、以下の命令で立ち上がり、立ち下がりのパラメータを各コンバータ毎に自在に設定することができます。

| PMBus命令 | 機能 |

|---|---|

| TON_DELAY | 立ち上がりディレイ時間の設定 |

| TON_RISE | 立ち上がり時間の設定 |

| TOFF_DELAY | 立ち下がりディレイ時間の設定 |