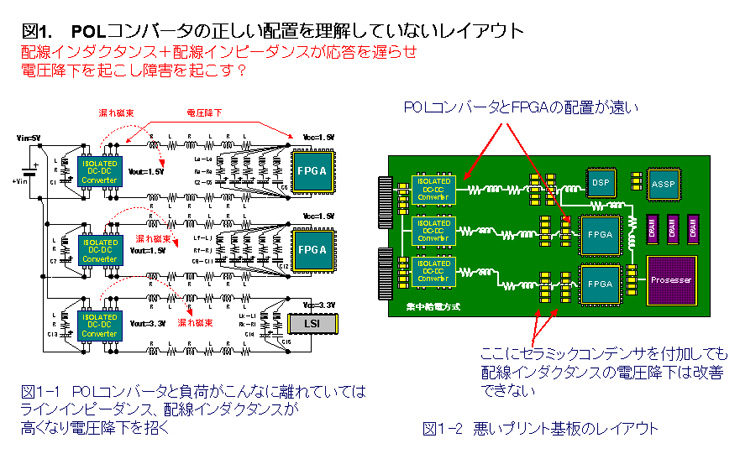

半導体の低電圧化でFPGAなど最新ICの駆動電圧が低電圧化しています。パターン幅60nm以下のFPGAのコア電源は1.2V付近まで低電圧化が進んでいます。図1-1はDC-DCコンバータをプリント基板のコネクタ近くに配置してあります。高精度FPGAやLSIをDC-DCコンバータから発生する輻射ノイズの影響を避ける目的でコンバータから離れた場所へ配置した例です。ロジック電圧=5Vの時代ではこの方法も悪くはありませんでした。しかし、低電圧化の現在ではDC-DCコンバータとFPGAなどの負荷間の配線インピーダンスと配線インダクタンスの影響で電圧降下を招き、コンバータの自身の電圧ディップと重なってICへの電圧は不足します。特に負荷電流が急峻な立上がり、立下がりのある高di/dtの場合にはFPGAのコア電圧あるいはI/O電圧が不足して電源異常でエラーを起こす事が考えられます。 図1-2はDC-DCコンバータと負荷であるFPGA間にコンデンサを入れた基板例です。高di/dtによる一瞬の電圧降下をコンデンサの容量で電圧を保持しょうとする目的ですが、負荷ICが大きなパワーを必要とするICではセラミックコンデンサ程度の容量では保持時間を確保する事は出来ません。 それではと、ここに大容量の電解コンデンサを付けると保持時間は確保される方向に向かいますが、システムの立ち上げの時に、この大容量のコンデンサへ充電のための突入電流が流れます。このときDC-DCコンバータの過電流保護領域に電流が流れて、FPGAは上がり電圧が遅延してしまい、FPGAはデーターを取り込めないエラーを招く事があります。 この図1-1、図1-2の回路、プリント基板レイアウト例は悪い配置例として見ていただきたいと思います。別頁に正しいPOLコンバータの配置を解説しますので参考にしてください。

鈴木正太郎