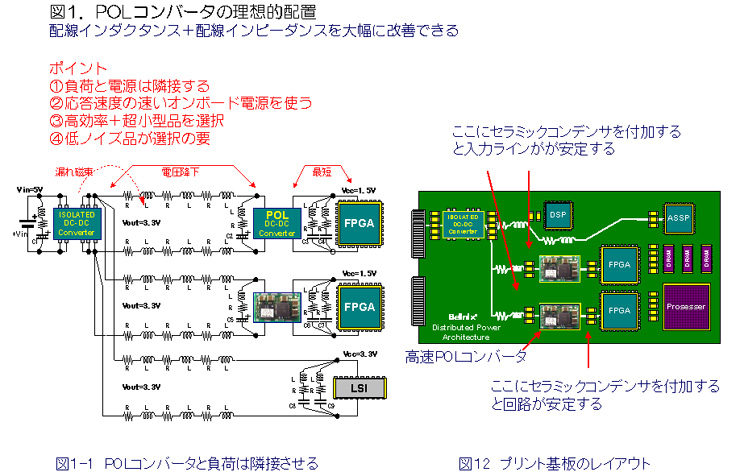

Point Of Load(POL)という言葉は古い用語ではありません。従来のロジック、あるいはデジタル電源電圧は「5V」というイメージは今でも定着しています。 最新のFPGAやLSIは半導体プロセスの進展で低電圧化が急速に進んでいます。新しいICではコア電源が1V付近まで低電圧化してきました。たとえば5V電源では±5%の変動が許されました。±5%は±250mVとなります。しかし最新のFPGAの電源は1.2V±2%程度まで高精度を要求される場合、1.2Vの±2%は±24mVとなります。これはDC-DCコンバータ自身の電圧変動と配線による電圧降下を合わせた電圧が±24mV以内に入っていなければならないという事になります。 これを実現する為には①POLコンバータの電圧ディップが小さいこと②オーバシュート、アンダーシュートが出ないPOLコンバータを選択する③プリント基板の設計では負荷(FPGA,LSIなど)に隣接してPOLコンバータを配置すること④ノイズが少なく高効率なPOLコンバータを選ぶ⑤実装時の放熱が容易な構造のPOLコンバータを選ぶ、などがポイントになりますが、どんなに良いPOLコンバータを選択してもプリント基板でのレイアウトしだいで折角の性能を引き出せないことになります。 図1-1では、絶縁型Brickコンバータ(あるいはBusコンバータ)をプリント基板のコネクタ近くに配し、POLコンバータは負荷であるFPGAやCPUに隣接して配置するイメージ図です。この配線図ではPOLコンバータを負荷の隣に配置すればBrickコンバータとPOLコンバータ間の配線インダクタンス、配線インピーダンスの影響は受けずに高精度なPOLコンバータの性能を引き出せる事になります。図1-2のプリント基板図でPOLコンバータの入力端とPOLコンバータと負荷間にセラミックコンデンサを負荷することをお勧めします。このコンデンサの付加は電源ラインのラインインピーダンスを下げて回路を安定化させる効果が期待できます。

鈴木正太郎