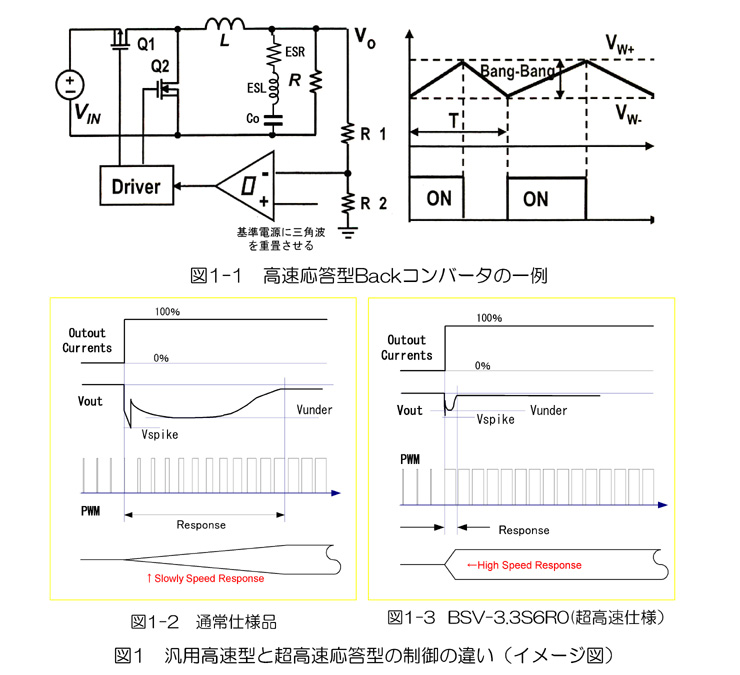

高速POLコンバータの設計は単に発振周波数を高くしてもできません。負荷が急変した時に従来のパルス幅(PMW)での負帰還回路では、出力の変化を検出して変調回路を経由してパルス幅制御が行われますが、誤差増幅器による位相遅れで図1-2の用に変調信号は徐々に伝わり制御されます。この非制御の期間、出力電圧はコンデンサC0の電荷で保たれます。従って急激に負荷に電流が流れるとコンデンサの放電で出力へ電流がながれますが、このコンデンサの等価抵抗(ESR)、リードインダクタンス(ESL)の大小が応答波形を決めてしまいます。

この時のΔVoutは

ΔVout=ΔVCout+ΔIo×RESR

Bang-Bang制御方式は、高速応答回路を作れます。図1の回路でヒステリシスコンパレータを使い誤差増幅器は使いません。この為、誤差増幅器の位相遅れが無い分制御速度が速くなります。このヒステリシスコンパレータは基準電圧に三角波を重畳させた電圧をコンパレータICのプラス端子に印加して出力Voutの変動電圧を検出するR1,R2の電圧を比較コンパレートする事で制御します。(図1-2) 図1-3は超高速タイプのPOLコンバータのPWM制御波形です。高速タイプは、急峻な負荷変動を検出して1個目のパルスで応答して高速制御がなされます。

鈴木正太郎

参考文献:ヒステリシスPWM制御方式を用いた降圧形コンバータについて 鍋島隆 日本学術振興会H16.10.26